MBEES 2018

MBEES 2018

MBEES 2018

MBEES 2018

MBEES 2018

# Tagungsband des Dagstuhl-Workshops

## Modellbasierte Entwicklung eingebetteter Systeme XIV

Matthias Riebisch Michaela Huhn Hardi Hungar Sebastian Voss

### **Tagungsband**

## Dagstuhl-Workshop MBEES: Modellbasierte Entwicklung eingebetteter Systeme XIV

Model-Based Development of Embedded Systems 16.04.2018 – 18.04.2018

fortiss GmbH Guerickestr. 25 80805 München

#### Organisationskomitee

Prof. Dr. Michaela Huhn, Ostfalia Hochschule für angewandte Wissenschaften

Prof. Dr.-Ing. habil. Matthias Riebisch, Universität Hamburg

PD Dr. Hardi Hungar, Deutsches Zentrum für Luft- und Raumfahrt

Dr. Sebastian Voss fortiss GmbH

#### **Programmkomitee**

Sibylle Froeschle, OFFIS & Universität Oldenburg

Michaela Huhn, Ostfalia Hochschule für angewandte Wissenschaften

Hardi Hungar, DLR

Matthias Riebisch, Universität Hamburg

Bernhard Rumpe, RWTH Aachen

Andy Schürr, TU Darmstadt

Andreas Vogelsang, TU Berlin

Sebastian Voss, fortiss GmbH

### Inhaltsverzeichnis

| Zum fehlenden Architekturverständnis über Implementierungsmodelle multifunktionaler eingebetteter Systeme in der industriellen Praxis  Timo Kehrer, Andreas Vogelsang, Thomas Vogel and Heiko Dörr | 1          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Qualification of Model-Based Development Tools - A Case Study<br>Mirko Conrad, Sophia Kohle and Hartmut Pohlheim                                                                                   | 7          |

| Feature-based Recommendation for Product Configuration in the Software Product Lines  Yibo Wang, Lothar Hotz and Matthias Riebisch                                                                 | 19         |

| Feature-oriented Domain-specific Languages  Philipp Ulsamer, Tobias Fertig and Peter Braun                                                                                                         | 31         |

| Using PLC Programming Languages for Test-Case Specification of Hardware-in-the-loop Tests  David Thönnessen and Stefan Kowalewski                                                                  | 41         |

| Finding Inconsistencies in Design Models and Requirements by Apply the SMARDT Process  Stefan Kriebel, Evgeny Kusmenko, Bernhard Rumpe and Michael von Wenckstern                                  | ring<br>51 |

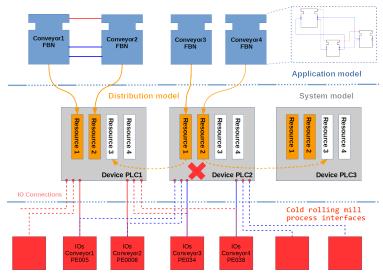

| Applying DSE for Solving the Deployment Problem in Industry 4.0  Tarik Terzimehic, Sebastian Voss, Monika Wenger and  Vincent Aravantinos                                                          | 61         |

| Exploration of hardware topologies and complexity reduction<br><i>Johannes Eder</i>                                                                                                                | 71         |

| Ein Mittel zur Wiederverwendung Komponentenbasierte Architektur                     | en |

|-------------------------------------------------------------------------------------|----|

| in der Automatisierungstechnik  Constantin Wagner, Julian Grothoff and Ulrich Epple | 81 |

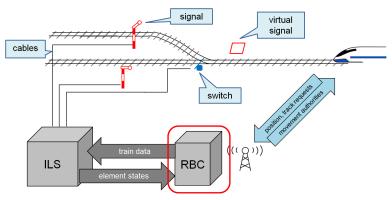

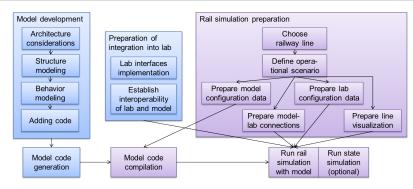

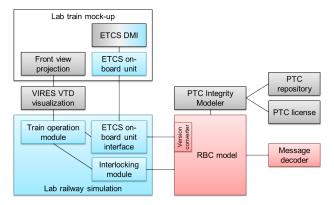

| Integrating a Signaling Component Model into a Railway Simulation  Daniel Schwencke | 87 |

Ostfalia

Hochschule für angewandte

Wissenschaften

Innerhalb der Gesellschaft für Informatik e.V. (GI) befasst sich eine große Anzahl von Fachgruppen explizit mit der Modellierung von Software- bzw. Informationssystemen. Der erst neu gegründete Querschnittsfachausschuss Modellierung der GI bietet den Mitgliedern dieser Fachgruppen der GI - wie auch nicht organisierten Wissenschaftlern und Praktikern - ein Forum, um gemeinsam aktuelle und zukünftige Themen der Modellierungsforschung zu erörtern und den gegenseitigen Erfahrungsaustausch zu stimulieren.

Das Institut für Software Engineering ist eine wissenschaftliche Einrichtung der Fakultät Informatik der Ostfalia, Hochschule für angewandte Wissenschaften. Die Forschungsschwerpunkte sind

- Entwicklung komplexer Systeme auf Basis von Java und Java EE

- Entwicklung webbasierter Oberflächen und mobiler Systeme

- Theoretische Grundlagen der Software-Entwicklung und formale Methoden

- Entwurfs- und Implementierungskonzepte für Software-Systeme

- Qualitätssicherung von Entwicklungsprozessen

- Modellgetriebene Software-Entwicklung

Die Anwendbarkeit der Lösungen wird immer wieder in industrienahen Projekten überprüft.

Schloss Dagstuhl wurde 1760 von dem damals regierenden Fürsten Graf Anton von Öttingen-Soetern-Hohenbaldern erbaut. 1989 erwarb das Saarland das Schloss zur Errichtung des Internationalen Begegnungs- und Forschungszentrums für Informatik. Das erste Seminar fand im August 1990 statt. Jährlich kommen ca. 2600 Wissenschaftler aus aller Welt zu 40-45 Seminaren und viele sonstigen Veranstaltungen.

fortiss ist das Forschungsinstitut des Freistaats Bayern für softwareintensive Systeme und Services mit Sitz in München. Das Institut beschäftigt derzeit rund 130 Mitarbeiter, die in Forschungs-, Entwicklungs- und Transferprojekten mit Universitäten und Technologie-Firmen in Bayern, Deutschland und Europa zusammenarbeiten.

Schwerpunkte sind die Erforschung modernster Methoden, Techniken und Werkzeuge der Softwareentwicklung, des Systems- & Service-Engineering und deren Anwendung auf verlässliche, sichere cyber-physische Systeme wie das Internet of Things (IoT). fortiss ist in der Rechtsform einer gemeinnützigen GmbH organisiert. Gesellschafter sind der Freistaat Bayern (als Mehrheitsgesellschafter) und die Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V..

Der Arbeitsbereich Softwareentwicklungs- und -konstruktionsmethoden SWK im Fachbereich Informatik der Universität Hamburg forscht auf dem Gebiet der Evolution von Softwaresystemen. Dazu gehören Arbeiten zu modellbasierter Softwareentwicklung, Softwarearchitekturen, Software-Reengineering sowie deren Einbettung in Entwicklungsprozesse. Das Ziel der Arbeiten sind ingenieurgemäße Vorgehensweisen und Methoden und deren Anwendbarkeit in der industriellen Praxis.

Das Deutsche Zentrum für Luft- und Raumfahrt (DLR) ist das Forschungszentrum der Bundesrepublik Deutschland für Luft- und Raumfahrt. Seine Forschungs- und Entwicklungsarbeiten in Luftfahrt, Raumfahrt, Energie, Verkehr, Digitalisierung und Sicherheit sind in nationale und internationale Kooperationen eingebunden.

Das Institut für Verkehrssystemtechnik ist eines der 36 Institute des DLR. Es betreibt Forschung und Entwicklung für Automobil- und Bahnsysteme und das Verkehrs- und Mobilitätsmanagement. Die Leitziele der Arbeit sind: Sicherheit, Effizienz, Nachhaltigkeit, Wirtschaftlichkeit und Qualität.

#### **Dagstuhl-Workshop MBEES:**

## Modellbasierte Entwicklung eingebetteter Systeme (Model-Based Development of Embedded Systems)

Die Bandbreite der Beiträge der diesjährigen Auflage der Dagstuhl-Workshopreihe "Modellbasierte Entwicklung eingebetteter Systeme" zeigt, dass Modelle in vielen Bereichen eine wichtige Rolle spielen, von der Beherrschung der Komplexität von Entwurfsaufgaben über die Validierung und Verifikation von Svstemen bis zur Generierung von Konfigurationen oder Software. Bei eingebetteten Systemen besteht eine besondere Herausforderung in der Modellierung über Plattform-, Technologie- und Hardware-Software-Grenzen hinweg. Die Spezifik solcher Systeme erfordert eine starke Anpassung von Modellierungssprachen an die Anforderungen der Domänen. Neue Entwicklungsrichtungen wie Industrie 4.0 und die Beherrschung der daraus resultierenden Datenmengen erfordern die Weiterentwicklung bisher bekannter Modellierungsansätze, beispielsweise bezüglich anwendungsorientierter Modelle mit domänenspezifischen Konzepten. Beiträge zur Weiterentwicklung des Stands der Forschung und zum Transfer in die industrielle Anwendung sind daher ein wesentliches Anliegen über die elf Ausgaben des Workshops hinweg. Der Fokus auf den- für eingebettete Systeme besonders wesentlichen - Bereich der Regelungs- und Steuerungstechnik stellt ein bedeutsames Ziel der industriellen modellbasierten Entwicklung dar.

Wie in den vorangehenden Jahren stellen die in diesem Tagungsband zusammengefassten Papiere sowohl gesicherte Ergebnisse, als auch Work-In-Progress, industrielle Erfahrungen und innovative Ideen aus diesem Bereich zusammen und erreichen damit eine interessante Mischung theoretischer Grundlagen und praxisbezogener Anwendung. Die breiter angelegten Diskussionsmöglichkeiten zielen auf eine Verstärkung des Austauschs zwischen solchen Ausrichtungen ab. Genau wie bei den vorhergehenden erfolgreich durchgeführten Workshops 2005 bis 2017 sind damit wesentliche Ziele dieses Workshops erreicht:

- Austausch über Probleme und existierende Ansätze zwischen den unterschiedlichen Disziplinen (insbesondere Elektro- und Informationstechnik, Maschinenwesen/Mechatronik, Automatisierungstechnik und Informatik)

- Austausch über relevante Probleme in der industriellen Anwendung und existierende Ansätze in der Forschung

- Verbindung zu nationalen und internationalen Aktivitäten (z.B. Initiative des IEEE zum Thema Model-Based Systems Engineering, GI-AK Modellbasierte Entwicklung eingebetteter Systeme, GI-FG Echtzeitprogrammierung, MDA Initiative der OMG)

Die Themengebiete, für die dieser Workshop gedacht ist, sind fachlich sehr gut abgedeckt. Die Beiträge adressieren verschiedenste Aspekte modellbasierter Entwicklung eingebetteter Softwaresysteme, unter anderem:

- Modelle in der architekturzentrierten Entwicklung und bei der Produktlinienentwicklung für Hardware-Software-Systeme und Software-intensive Systeme

- Domänenspezifische Ansätze zur Modellierung von Systemen

- Modellbasierte Validierung, Verifikation und Diagnose

- Modellierung zwecks Simulation von Systemverhalten zur Laufzeit

- Bewertung der Qualität von Modellen

- Funktionale Sicherheit und modellbasierte Entwicklung

- Evolution von Modellen

- Einbindung von Modellbasierten Entwicklung in Entwicklungsprozesse

Das Organisationskomitee ist der Meinung, dass mit den Teilnehmern aus Industrie, Werkzeugherstellern und der Wissenschaft die bereits seit 2005 erfolgte Community-Bildung erfolgreich weitergeführt wurde. Der nunmehr zwölfte MBEES Workshop belegt, dass eine solide Basis zur Weiterentwicklung des Themas modellbasierter Entwicklung eingebetteter Systeme existiert. Der hohe Anteil von deutschen Forschern und Entwicklern an den einschlägigen internationalen Konferenzreihen zu Modellierung und Cyperphysical Systems zeigt, dass die deutsche Zusammenarbeit in diesem Themenfeld Früchte getragen hat.

Die Durchführung eines erfolgreichen Workshops ist ohne vielfache Unterstützung nicht möglich. Wir danken daher den Mitarbeitern von Schloss Dagstuhl.

Schloss Dagstuhl im März 2018,

#### **Das Organisationskomitee:**

Michaela Huhn, Ostfalia Hochschule für angewandte Wissenschaften

Hardi Hungar, DLR

Matthias Riebisch, Uni Hamburg

Sebastian Voss, fortiss GmbH

Mit Unterstützung von

Tarik Terzimehic, fortiss GmbH

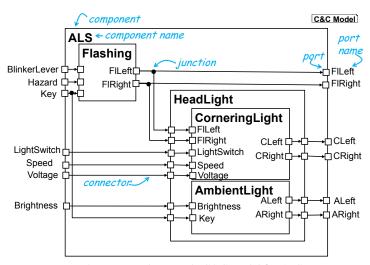

#### Zum fehlenden Architekturverständnis über Implementierungsmodelle multifunktionaler eingebetteter Systeme in der industriellen Praxis

Timo Kehrer<sup>1</sup>, Andreas Vogelsang<sup>2</sup>, Thomas Vogel<sup>3</sup>, Heiko Dörr<sup>4</sup>

Abstract: Klassische eingebettete Systeme werden zunehmend zu autonomen und offenen Systemen, die auf ihre Umwelt reagieren und im Verbund mit anderen Systemen übergeordnete Ziele verfolgen. Modellbildung ist ein vielversprechender Ansatz, die Komplexität solcher multifunktionalen Systeme zu beherrschen. Auf der Ebene der Teilfunktionen hat sich Matlab-Simulink in vielen Unternehmen, bspw. in der Automobilbranche, als de-facto Standard für die modellbasierte Entwicklung von eingebetteten Systemen etabliert. Die Implementierungsmodelle der Teilfunktionen werden jedoch arbeitsteilig entwickelt und erst spät im Entwicklungsprozess zu einem Gesamtsystem integriert. Ein Gesamtsystem wird somit durch eine Menge lose gekoppelter Simulink-Modelle beschrieben, das Wissen über deren Kommunikationsbeziehungen ist lediglich implizit vorhanden und geht im Zuge der Softwareevolution zunehmend verloren. Bei der Integration kommt es daher häufig zu unerwünschtem und oftmals nicht vorhergesehenem Verhalten. Eine Analyse der entsprechenden Interaktionen einzelner Teilfunktionen ist derzeit lediglich auf Basis des generierten Quellcodes möglich. Dies steht jedoch in eklatantem Widerspruch zum Paradigma der modellbasierten Softwareentwicklung und führt zu hohen Integrationskosten. In diesem Papier analysieren wir diese Problematik des fehlenden "architektonischen" Verständnis über eine Menge von Implementierungsmodellen und stellen unser Forschungsvorhaben zur Anhebung von funktionsübergreifenden Analysen auf die Modellebene vor.

#### 1 Einführung

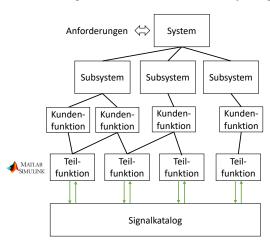

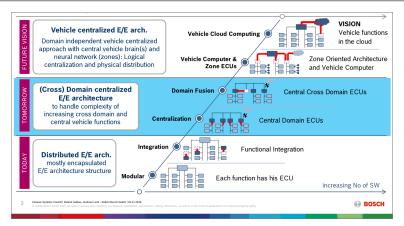

Klassische eingebettete Systeme entwickeln sich zunehmend zu autonomen und offenen Systemen, die auf ihre Umwelt reagieren und im Verbund mit anderen Systemen übergeordnete Ziele verfolgen. Dabei übernehmen einzelne Systeme immer mehr und vielfältigere Aufgaben und werden somit zu multifunktionalen Systemen [1]. Abb. 1 zeigt eine exemplarische Übersicht, wie die Entwicklung von multifunktionalen Systemen heute typischerweise aus Sicht eines Herstellers (engl. Original Equipment Manufacturer (OEM)) strukturiert ist. Ein komplexes System wird zunächst zerlegt in Subsysteme, welche die einzelnen Funktionen thematisch gruppieren. Im Fahrzeugbau wird oft von Domänen gesprochen

<sup>&</sup>lt;sup>4</sup> Model Engineering Solutions GmbH. doerr@model-engineers.com

Institut für Informatik, Humboldt-Universität zu Berlin. timo.kehrer@informatik.hu-berlin.de

<sup>&</sup>lt;sup>2</sup> Fachgebiet IT-basierte Fahrzeuginnovationen, Technische Universität Berlin. andreas.vogelsang@tu-berlin.de

<sup>&</sup>lt;sup>3</sup> Institut für Informatik, Humboldt-Universität zu Berlin. thomas.vogelinformatik.hu-berlin.de

(Karosserie, Antriebsstrang, Fahrerassistenz, Infotainment, etc.). Im Rahmen eines Teilsystems werden dann eine Reihe von *Kundenfunktionen* spezifiziert. Eine Kundenfunktion beschreibt ein gewünschtes Verhalten an der Systemgrenze, z.B. durch Kunden wahrnehmbar.

Abb. 1: Zerlegung eines multifunktionalen Systems.

Der Begriff Kunde ist hier breit gefasst und enthält alle externen Systeme und Aktoren, die mit dem zu entwickelnden System interagieren. Kundenfunktionen werden weiter heruntergebrochen in einzelne Teilfunktionen, welche die Kundenfunktionen dann realisieren, indem sie Signale verarbeiten und daraus neue Signale erzeugen. Die im System verfügbaren Signale sind in einem Signalkatalog erfasst. Wenn zu den Teilfunktionen, die an der Realisierung einer Kundenfunktion beteiligt sind auch noch deren Abhängigkeiten dokumentiert werden, dann spricht man auch von einer Wirkkette. Wirkketten stellen also

eine partielle Sicht auf die Architektur der Teilfunktionen und deren Abhängigkeiten dar.

Modellbildung ist ein vielversprechender Ansatz, die Komplexität von multifunktionalen Systemen zu beherrschen. Auf der Ebene der Teilfunktionen setzen Unternehmen verstärkt auf *modellbasierte Entwicklung*, wobei sich Matlab Simulink<sup>5</sup> als de-facto Standard für die modellbasierte Entwicklung von eingebetteten Systemen etabliert hat. In Simulink wird das Verhalten einer Teilfunktion mit Hilfe eines datenflussorientierten Modells beschrieben. Aus diesem *Implementierungsmodell* kann später automatisch Code erzeugt werden, der auf einem Steuergerät ausgeführt wird und das gewünschte Verhalten erbringt. Die Implementierungsmodelle der Teilfunktionen eines multifunktionalen Systems werden jedoch arbeitsteilig und meist in unterschiedlichen Abteilungen eines Unternehmens entwickelt und erst sehr spät im Entwicklungsprozess zu einem Gesamtsystem integriert. Ein Gesamtsystem wird somit durch eine Menge lose gekoppelter und autark entwickelter Simulink-Modelle beschrieben, das Wissen über deren Kommunikationsbeziehungen ist lediglich implizit vorhanden. Bei der Integration kommt es daher häufig zu ungewünschtem, nicht vorhergesehenem Verhalten, so dass Integrations- und Testaktivitäten heute einen Großteil der Kosten bei der Entwicklung von eingebetteten Systemen verursachen [2].

In Abschnitt 2 analysieren wir die Problematik des fehlenden "architektonischen" Verständnis über eine Menge von Implementierungsmodellen, welches wir insbesondere auf das Fehlen von frühen und funktionsübergreifenden Analysen auf Modellebene zurückführen. Daraus leiten wir in Abschnitt 3 unser Forschungsvorhaben zur konsequenten Anhebung aller

<sup>5</sup> https://de.mathworks.com/products/simulink.html

integrativen Analysetätigkeiten auf die Modellebene ab. Eine Auswahl an alternativen Ansätzen beleuchten wir in Abschnitt 4 und resümieren unser Positionspapier in Abschnitt 5.

#### 2 Problemanalyse

Die Kosten für die Integration und den Test multifunktionaler eingebetteter Systeme sind heute trotz modellbasierter Entwicklungsansätze sehr hoch. Kernhypothese unseres Forschungsvorhabens ist, dass dies i.W. auf das fehlende architektonische Verständnis über eine Menge lose gekoppelter Implementierungsmodelle zurückzuführen ist.

Eine Integration der Teilfunktionen findet erst auf Code- bzw. Geräteebene und damit sehr spät im Entwicklungsprozess statt, so dass Abhängigkeiten zwischen diesen Teilfunktionen in den früheren Phasen der Entwicklung nicht berücksichtigt werden. Es gibt keine explizite Verwaltung und Kontrolle über die Abhängigkeiten. In Vorarbeiten haben wir festgestellt, dass vermeintlich unabhängige Kundenfunktionen im Automobilbereich auf der Ebene der Teilfunktionen hochgradig vernetzt sind [3], ca. die Hälfte aller Abhängigkeiten zwischen Kundenfunktionen waren den Entwicklern unbekannt. In einem untersuchten Projekt im Bereich Automotive Infotainment war das fehlende Verständnis über die Interaktionen der Teilfunktionen die Ursache für mehr als 40% aller Fehler [4]. Ferner werden die Schnittstellendefinitionen der Teilfunktionen in vielen Fällen in den Implementierungsmodellen nicht eingehalten und es existieren keine Ansätze, um diese Abweichungen kontinuierlich zu prüfen. Feilkas et al. [5] berichten über drei industrielle Fallstudien in denen bis zu 19% aller Abhängigkeiten in der Implementierung von der ursprünglich spezifizierten Architektur abweichen. Dabei war in vielen Fällen den Entwicklern nicht klar, ob es sich bei diesen Abweichungen um Fehler in der Spezifikation oder in der Implementierung handelt. Auch Wirkketten werden in der Praxis häufig nur zur Spezifikation von Kundenfunktionen genutzt. Eine Verifikation der implementierten Architektur gegenüber spezifizierten Wirkketten bleibt häufig aus. Hinzu kommt, dass die Spezifikation mit Hilfe von Wirkketten den Blick für Abhängigkeiten zwischen Wirkketten trübt. Abhängigkeiten zwischen Teilfunktionen unterschiedlicher Wirkketten sind in der implementierten Architektur vorhanden, spiegeln sich aber nicht in den spezifizierten Wirkketten wieder.

Zusammenfassend lässt sich sagen, dass der Einsatz von Modellbasierung zur frühen Fehlervermeidung und Reduzierung von Integrations- und Testkosten zwar vielversprechend ist, das volle Potential aber erst ausgeschöpft werden kann, wenn die erstellten Implementierungsmodelle auch modellübergreifend analysiert werden und kontinuierlich auf Abweichungen gegenüber abstrakteren Spezifikationen geprüft werden.

#### 3 Forschungsvorhaben

Übergeordnetes Ziel unseres Forschungsvorhabens ist die Entwicklung von strukturbasierten Verfahren zur Analyse der Architektur aller kommunizierenden Implementierungsmodelle,

mit denen sich mögliche Integrationsrisiken frühzeitig erkennen lassen. Dies umfasst die Identifikation und Erkennung von Architektur-Smells und Anti-Patterns, sowie die Verifikation gegenüber funktionsübergreifenden, strukturellen Spezifikationen wie bspw. Wirkketten. Grundlage aller modellbasierten Analysen bildet die tatsächlich vorliegende Architektur über einer Menge autark entwickelter Implementierungsmodelle, welche in einem ersten Reverse Engineering Schritt anhand der impliziten Abhängigkeiten zwischen den kommunizierenden Implementierungsmodellen gewonnen werden soll. Die Art und Granularität der extrahierten Architekturmodelle richten sich nach den jeweiligen Analysen. Da Simulink-Modelle oft als Basis für die Codegenerierung dienen, werden diese in der Regel sehr gut gepflegt und aktuell gehalten. Wir planen daher mit unseren Analysen auf einer Menge von bestehenden Simulink-Modellen aufzusetzen, die jeweils eine Teilfunktion beschreiben. Es ist geplant, die Analysen in das Qualitätssicherungswerkzeug MES M-XRAY<sup>6</sup> einzubetten. Die entwickelten Verfahren sind jedoch auch auf andere blockorientierte Modelltypen wie bspw. Komponenten- und Konnektormodelle [6] übertragbar.

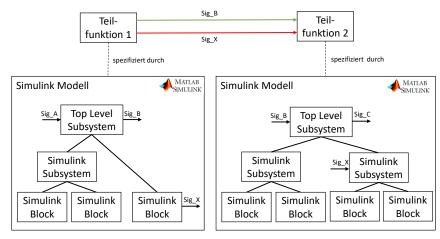

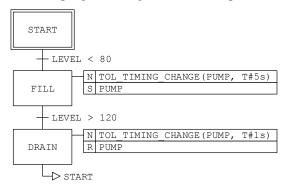

Ein Beispielszenario für die Verifikation einer Implementierungsarchitektur ist deren Konformanzprüfung gegenüber der spezifizierten Soll-Architektur, welche sich bspw. aus den Schnittstellendefinitionen der Software-Komponenten zur Realisierung von Teilfunktionen ableiten lässt. In Matlab-Simulink werden zur Schnittstellenspezifikation einer Teilfunktion oftmals die Ein- und Ausgaben (d.h. die Input- und Outputsignale) des Top-Level Subsystems des entsprechenden Simulink-Modells verwendet. Eine Soll-Architektur resultiert somit implizit aus den dadurch festgelegten Abhängigkeiten zwischen den verschiedenen Simulink-Modellen. Im Beispiel in Abb. 2 enthält die Soll-Architektur eine Abhängigkeit zwischen Teilfunktion 1 und Teilfunktion 2 über das Signal  $Sig_B$ . Zur Extraktion des tatsächlichen Architekturmodells steigen wir tiefer in den hierarchischen Simulink-Modellen hinab und interpretieren diese als Implementierung einer Teilfunktion. Wir analysieren, in wie weit hier zusätzliche Abhängigkeiten vorhanden sind, die auf dem Top-Level Subsystem nicht berücksichtigt wurden. Diese impliziten Abhängigkeiten stellen potentielle Verletzungen der Ist-Architektur gegenüber der Soll-Architektur dar (im Beispiel die implizite Abhängigkeit über das Signal  $Sig_A$ ).

Eine offene Forschungsfrage ist, inwiefern Integrationsfehler tatsächlich mit architektonischen Schwachstellen wie der oben skizzierten Abweichung von Soll- und Ist-Architekturen korrelieren. Ähnliche Fragen ergeben sich für Architektur-Smells, Anti-Patterns sowie für negative Ergebnisse bei der Verifikation von Wirkketten. Dies soll in empirischen Studien in Kooperation mit unserem assoziierten Partner aus dem Bereich Automotive untersucht werden. Auf unseren Forschungsergebnissen aufbauend wollen wir ferner Verfahren zur Bewertung von Integrationsrisiken und schließlich auch zu deren geeigneter Behandlung entwickeln.

<sup>6</sup> https://www.model-engineers.com/de/m-xray.html

Abb. 2: Extraktion einer Soll- und Ist-Architektur durch Analyse von Simulink-Modellen.

#### Alternative Ansätze und verwandte Arbeiten

In der Praxis sind Verfahren zum Reverse Engineerung von Architekturen aus Implementierungsmodellen sowie darauf aufbauende, modellbasierte Analysen nicht etabliert. Vielmehr werden aktuell Ansätze zum Forward-Engineering von Software-Architekturen unter Einsatz klassischer UML-basierter Notationen erprobt. Jedoch haben diese Modelle häufig nur einen Dokumentationscharakter und dienen nicht als technische Grundlage für die Implementierung. Weiterhin werden spezielle Architekturdatenbanken eingesetzt, aus denen Architekturspezifikationen für einzelne Simulink-Modelle gewonnen werden können. Alle Ansätze haben gemein, dass ein nachträglicher Architekturabgleich nicht konstruktiv unterstützt wird. Analysewerkzeuge für Implementierungsmodelle sind zwar bereits verfügbar, unterstützen jedoch lediglich die Analyse einzelner, autonomer Modelle. Ein Beispiel für ein ausgereiftes Analysewerkzeug für einzelne Simulink-Modelle ist MES M-XRAY, modellübergreifende Analysen werden bislang jedoch nicht unterstützt.

Aus Forschungsperspektive mit unserem Ansatz vergleichbar ist die in [7] skizzierte Idee des "kontinuierlichen Reverse Engineering" und der stetigen Konformanzprüfung der extrahierten Modelle zu dem entsprechenden Quellcode. Extrahiert werden hier jedoch klassische, aus der Objektorientierung bekannte Modelltypen. In [8] werden Abhängigkeitsgraphen aus Simulink-Modellen erzeugt, allerdings auf Basis eines einzelnen Simulink-Modells und mit dem Ziel der automatisierten Testfallgenerierung. Modelle über Soll- und Ist-Architekturen lassen sich als zwar als co-evolvierende Modelle auffassen, existierende Analysen von co-evolvierenden Modellen konzentrieren sich meist auf Änderungen in klassischen Multi-View-Modellen [9]. Ansätze zur Verifikation von Implementierungsmodellen gegenüber abstrakten Spezifikationen fokussieren sich wie die in [6] vorgestellte Methode auf die Formalisierung und Verifikation von Anforderungsspezifikationen, und wurden bislang ebenfalls nur auf einzelne Implementierungsmodelle angewendet.

#### 5 Resümee

Trotz modellbasierter Methoden ist die Entwicklung multifunktionaler eingebetteter Systeme eine überaus aktuelle Herausforderung. Ein Gesamtsystem wird in der Praxis meist durch eine Menge lose gekoppelter Simulink-Modelle beschrieben, ein architektonisches Verständnis über deren Kommunikationsbeziehungen ist lediglich implizit vorhanden, was zu hohen Integrationskosten führt. Ziel unseres Forschungsvorhabens ist die Entwicklung von strukturbasierten Verfahren zur Analyse der Architektur aller kommunizierenden Implementierungsmodelle, mit denen sich mögliche Integrationsrisiken frühzeitig erkennen, bewerten und letzten Endes auch behandeln lassen.

#### Literatur

- [1] Manfred Broy. "Multifunctional software systems: Structured modeling and specification of functional requirements". In: *Science of Computer Programming* 75.12 (2010).

- [2] Claudiu Farcas u. a. "Addressing the Integration Challenge for Avionics and Automotive Systems—From Components to Rich Services". In: *Proc. of the IEEE* 98.4 (2010), S. 562–583.

- [3] Andreas Vogelsang und Steffen Fuhrmann. "Why Feature Dependencies Challenge the Requirements Engineering of Automotive Systems: An Empirical Study". In: *Proc. IEEE International Requirements Engineering Conference (RE'13)*. 2013.

- [4] Sebastian Benz. "Generating Tests for Feature Interaction". Diss. Technische Universität München, 2010.

- [5] Martin Feilkas, Daniel Ratiu und Elmar Jurgens. "The loss of architectural knowledge during system evolution: An industrial case study". In: *International Conference on Program Comprehension (ICPC)*. IEEE. 2009, S. 188–197.

- [6] Vincent Bertram u. a. "Component and Connector Views in Practice: An Experience Report". In: 2017 ACM/IEEE 20th International Conference on Model Driven Engineering Languages and Systems (MODELS). IEEE. 2017, S. 167–177.

- [7] Gerardo Canfora, Massimiliano Di Penta und Luigi Cerulo. "Achievements and Challenges in Software Reverse Engineering". In: *Commun. ACM* 54.4 (2011).

- [8] Adepu Sridhar, D. Srinivasulu und Durga P. Mohapatra. "Model-based test-case generation for Simulink/Stateflow using dependency graph approach". In: *IEEE International Advance Computing Conference (IACC)*. 2013.

- [9] Sinem Getir, Michaela Rindt und Timo Kehrer. "A Generic Framework for Analyzing Model Co-Evolution." In: *ME* @ *MoDELS*. 2014.

## **Qualification of Model-Based Development Tools**

A Case Study

Mirko Conrad¹

samoconsult GmbH

mirko.conrad@samoconsult.de

Sophia Kohle, Hartmut Pohlheim Model Engineering Solutions GmbH sophia.kohle@model-engineers.com pohlheim@model-engineers.com

**Abstract:** Modern functional safety standards typically provide objectives or requirements on how to gain confidence in development tools used for electric and/or electronic systems. The corresponding approaches are referred to as tool qualification, tool validation, or tool certification.

To gain confidence in the tools used to develop automotive E/E systems, the ISO 26262 standard outlines a two-step approach consisting of tool classification potentially followed by tool qualification.

Although some research about ISO 26262 tool classification has been published, information about the tool qualification part is rather limited. This paper intends to reduce this gap by reporting on the qualification of MXAM, a static analysis tool for Simulink/TargetLink models.

#### 1 Introduction

Software tools are widely used in multiple domains to assist in developing or verifying electric and/or electronic systems (E/E systems). In E/E system development, such tools can assist with analysis and potentially improve system safety by automating the activities performed and by predictably performing tasks that may be prone to human error. On the contrary, an error in a tool may have a negative impact on safety if the tool inadequately performs its intended functions (cf. [DO 330]).

To reduce the potential risks associated with tool usage and to ensure the integrity of the tool functionality, recent (functional) safety standards call for dedicated activities to gain confidence in the tools used in the development of E/E systems. Depending on the domain or standard, the corresponding approaches are referred to as tool validation, tool qualification, or tool certification.

For the development of automotive E/E systems, the pertinent functional safety standard is ISO 26262 [ISO 26262]. Part 8 of this standard calls for a two-step process to gain

<sup>&</sup>lt;sup>1</sup> https://orcid.org/0000-0003-3221-6503

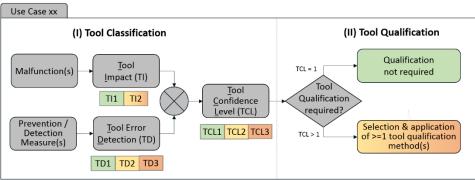

confidence in software tools. It starts with (I) tool classification to determine the required level of confidence in each software tool. Depending on the outcome of the first step, (II) a subsequent tool qualification process to establish the required confidence might be necessary.

When ISO 26262 came into effect in 2011, tool classification and qualification changed from a niche topic to a mainstream requirement for automotive OEMs, their suppliers, and software tool vendors. In the meantime, practitioners gained quite a bit of experience with tool classification (see e.g., [Mai09], [CMR10], [Con10], [KKG10], [CF11], [HK11], [Spä14], and [CF15]). Tool support for the ISO 26262 tool classification activities is available by means of dedicated Excel templates [Con14], [Con16], or the Tool Chain Analyzer [SWP+12].

Actionable advice on tool qualification is – despite some general observations regarding this topic (see e.g. [SWP+12]), work-share considerations (see e.g., [CMR10], [CSM11]), or tool type-specific advice mostly for code generators and compilers (see e.g., [SS07], [SCD07], [Glö08], [SML08], [KKG10]) – still lacking.

By outlining the approach taken to qualify the MES Model Examiner® (MXAM), a static analysis tool/guideline checker for executable models used in the development of automotive E/E systems, the authors aim to widen the accessible body of information on this topic.

## 2 Gaining Confidence in the Use of Software Tools – The ISO 26262 Approach

The two-step approach to gaining confidence in the use of software tools required as per ISO 26262 is illustrated in Figure 1

Figure 1: Two-step approach to gaining confidence in the software tools used.

#### 2.1 Tool Classification

Tool classification is based on the actual/intended usage of the tool. Therefore, the tool usage needs to be documented by means of tool use cases. Each of the use cases is subjected to further analysis.

First, potential malfunctions of the tool that could occur in the context of the use case at hand need to be identified and documented. For each malfunction, it needs to be determined whether the tool could introduce errors into the E/E system under development or fail to detect such errors. If it can be argued that there is no such possibility, the malfunction has a tool impact of 1 (TI1), otherwise the tool impact is 2 (TI2). If all malfunctions in the context of a given use case are rated TI1, the entire use case can be considered TI1.

Second, the measures applied to prevent or detect these malfunctions or their resulting erroneous output need to be documented and the confidence in these measures needs to be rated. Depending on whether there is high, medium, or even low confidence, the tool error detection is 1 (TD1), 2 (TD2), or 3 (TD3) respectively. In addition to the error detection of the individual measures, the tool error detection of a combination of measures might be rated [Con16]<sup>2</sup>.

Third, a tool confidence level (TCL) is assigned to each combination of a tool use case and a corresponding tool malfunction. Given a tool impact class (i.e., TI1 or TI2) and a tool error detection class (i.e., TD1, TD2, or TD3), the corresponding TCL can be derived according to Table 1 [ISO26262].

Table 1 Determination of the Tool Confidence Level (TCL).

| Tool Error Detection Tool Impact | TD1  | TD2  | TD3  |

|----------------------------------|------|------|------|

| TII                              | TCL1 | TCL1 | TCL1 |

| TI2                              | TCL1 | TCL2 | TCL3 |

Those combinations of use cases and malfunctions rated as TCL1 do not require further action. For all other combinations, i.e. those rated TCL2 or TCL3, the tool qualification process needs to be initiated. The tool classification step is documented in a tool criteria evaluation report (a.k.a. tool classification report).

#### 2.2 Tool Qualification

As per ISO 26262, tool qualification shall be carried out using a suitable combination of the following four tool qualification methods:

<sup>&</sup>lt;sup>2</sup> A combination of orthogonal detection measures might have better error detection capability than each of the individual measures. Rating such measure combinations requires engineering judgement and cannot be automated.

- a) Increased confidence from use.

- b) Evaluation of the tool development process.

- c) Validation of the software tool.

- d) Development in compliance with a safety standard.

The selection of appropriate tool qualification methods depends on the TCL and on the Automotive Safety Integrity Level (ASIL) of the E/E system to be developed.

However, the practical significance of tool qualification methods a)<sup>3</sup> and d) is rather limited<sup>4</sup>. The vast majority of all tool qualification approaches known to the authors use method b) or c) or a combination thereof.

If the method b) 'Evaluation of the tool development process' is applied to qualify a software tool, its tool development process shall comply with an appropriate standard. The tool development process shall be assessed based on an appropriate national or international standard (e.g., Automotive SPICE, CMMI, or ISO 15504) and the proper application of the assessed development process shall be demonstrated.

If the method c) 'Validation of the software tool' is utilized, the validation of the software tool shall meet three criteria:

- a) It shall be demonstrated that the software tool complies with its specified requirements, e.g., by using validation tests or reviews designed to evaluate functional and non-functional quality aspects of the tool.

- b) If malfunctions occur during the validation, these malfunctions and the resulting erroneous outputs shall be analyzed. Also, information on their possible consequences and measures to avoid or detect them shall be provided.

- c) The reaction of the software tool to anomalous operating conditions (e.g., fore-seeable misuse, incomplete input data, and incompatible combinations of configuration settings) shall be examined.

The tool qualification step is documented in a tool qualification report.

#### 3 Case Study: MXAM Qualification Kit

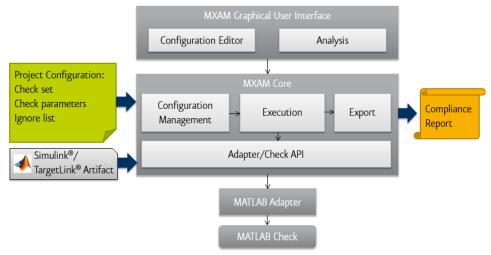

When utilizing the model-based development paradigm to develop automotive E/E systems, software units can be designed by means of executable Simulink or TargetLink models. Prior to code generation, the unit design needs to be statically analyzed to verify compliance with the applicable modeling guidelines. Modeling guideline checking can be carried out using MXAM.

<sup>&</sup>lt;sup>3</sup> Although a) sounds promising, it is rarely applicable due to frequent changes/updates to the tools being used.

<sup>&</sup>lt;sup>4</sup> Given the number and variety of development tools for E/E systems, proof of formal correctness could replace or extend the listed qualification methods for only a small subset of these tools.

#### 3.1 The MES Model Examiner® DRIVE

Using data and control flow analysis, MXAM checks Simulink or TargetLink models for aspects of functional safety, such as strong data typing, appropriate scaling and ranges of data, naming conventions, and layout.

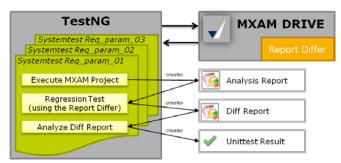

Figure 2: Architectural components of MXAM.

MXAM consists of a framework providing general functionalities such as GUI, management of projects and guidelines and checks, repair actions, and reporting. Further, dependent on the platform, guideline checks are provided or can be implemented by the tool user (cf. Figure 2). These checks comprise a description and an implementation.

#### 3.2 Tool Usage, Malfunctions, and Prevention/Detection Measures

The tool criteria evaluation report for MXAM that ships with the MXAM ISO 26262 Qualification Kit (cf. [Ko18]) analyzes four main uses cases, including:

• [UC\_MXAM01] Design Model – Modeling Guidelines Compliance Check.

Two potential malfunctions associated with the above use case will be used to illustrate the MXAM qualification approach in this paper:

- a) [E\_MXAM02] Modeling Guidelines Compliance Check: Violation not found.

- b) [E\_MXAM07] Modeling Guidelines Compliance Check: Usage of incorrect check parameters.

Certain malfunctions are overarching and thus check-agnostic. Corresponding qualification activities are check-agnostic as well. Other malfunctions have check-specific aspects and thus require check-specific qualification activities. Table 2, Table 3, and Table 4 illustrate how this part of tool classification is documented in the qualification kit.

[E\_MXAM02]: To detect [E\_MXAM02] in the context of [UC\_MXAM01], subsequent dynamic testing of the model under analysis can be applied ([M\_MXAM01]). However, the probability of detecting such a tool error with [M\_MXAM01] is considered to be medium and therefore the detection level is limited to TD2.

Additional subsequent guideline checking of the implementation model [M\_MXAM03] is another measure to counter [E\_MXAM02]. Again, this method can detect certain but not all instances of [E\_MXAM02] and is therefore rated as TD2 as well.

Table 2: Tool Classification Example I ([UC\_MXAM01] x [E\_MXAM02])

| Potential<br>Malfunction                                                           | TI  | Prevention/Detection<br>Measure                                                                                        | TD  | Justification for TD                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [E_MXAM02]<br>Modeling Guide-<br>lines Compliance<br>Check: Violation<br>not found | TI2 | [M_MXAM01]<br>Subsequent dynamic<br>testing of the model un-<br>der analysis                                           | TD2 | Guideline violation does not always result in in-<br>correct or unintended model functionality.<br>Actual model errors can be revealed by dynamic<br>testing ('medium' likelihood of error detection).                                                                                                    |

|                                                                                    |     | [M_MXAM03]<br>Subsequent modeling<br>guidelines checking of a<br>downstream model, e.g.<br>the implementation<br>model | TD2 | Subsequent static checking of the implementation model provides another means to identify guideline violations. However, if a check fails to detect a violation in the design model, it may fail to identify the same issue in the implementation model as well ('medium' likelihood of error detection). |

|                                                                                    |     | MEASURE<br>COMBINATION                                                                                                 | TD2 | TCL 2 ▷ Addressed by MXAM ISO 26262<br>Qualification Kit.                                                                                                                                                                                                                                                 |

Even if both measures are combined, a tool error detection better than TD2 could not be achieved. As a result, the tool confidence level for [E\_MXAM02] in the context of [UC\_MXAM01] is TCL2 and the combination [UC\_MXAM01] x [E\_MXAM02] needs to be subjected to tool qualification.

Without a tool-vendor-provided qualification kit, the tool user would need to qualify [UC\_MXAM01] x [E\_MXAM02], e.g., by validating the underlying MXAM functionality with a test suite. In the case of MXAM, this burden on the user is eased by the MXAM ISO 26262 Qualification Kit<sup>5</sup>.

[E\_MXAM07]: The second potential malfunction addresses that the check implementation could receive parameters from the MXAM framework that differ from the ones specified by the user (see Table 3). The default check parameters can be overwritten on several levels by the user (e.g., project, document, guideline level). The error that is addressed here might occur due to a defect in the overwrite algorithm that is common to all checks

<sup>&</sup>lt;sup>5</sup> Please note the lower right cell in Table 2 indicating that the tool user can leverage the qualification kit.

(i.e. check-agnostic). Malfunctions in the check-specific handling of check parameters are covered by [E\_MXAM02].

Table 3: Tool Classification Example II ([UC\_MXAM01] x [E\_MXAM07] – Initial Classification)

| Potential Malfunction                                                                             | TI  | Error Prevention/<br>Detection Measure                     | TD  | Justification for TD                                                                                                             |

|---------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------|

| [E_MXAM07]<br>Modeling Guidelines Com-<br>pliance Check: Usage of in-<br>correct check parameters | TI2 | [M_MXAM13]<br>Review of parameter<br>specification details | TD1 | Review of the parameter specifi-<br>cation details ensures the correct-<br>ness of the guideline check<br>parameters to be used. |

|                                                                                                   |     | [M_MXAM11]<br>Check for Error Messages                     | TD2 | Checking logs and compliance reports for error messages helps to detect anomalies such as an incorrect parameter definition.     |

|                                                                                                   |     | MEASURE<br>COMBINATION                                     | TD1 | TCL 1                                                                                                                            |

Malfunction [E\_MXAM07] could be mitigated by reviewing the parameter specification details provided by MXAM ([M\_MXAM13]) as these document the actual check parameters used during check execution. Thus, sufficient error prevention is possible (TCL1, cf. Table 3), but the necessary review activities would be very time consuming as they need to be performed for each individual overwritten parameter.

To reduce the amount of necessary prevention/detection activities for the tool user, the MXAM ISO 26262 Qualification Kit covers [E\_MXAM07] as well, meaning that [M\_MXAM13] does not need to be carried out any more. Hence, the effort required by the user to review every check parameter (currently more than 250 in the standard edition) for each project has been replaced by a qualification activity to be carried out by the tool vendor. This is reflected in the revised classification provided in Table 4.

Table 4: Tool Classification Example II ([UC\_MXAM01] x [E\_MXAM07] – Revised Classification)

| Potential Malfunction                                                                             | TI  | Error Prevention/<br>Detection Measure    | TD  | Justification for TD                                                                                                                      |

|---------------------------------------------------------------------------------------------------|-----|-------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| [E_MXAM07]<br>Modeling Guidelines Com-<br>pliance Check: Usage of in-<br>correct check parameters | TI2 | [M_MXAM11]<br>Check for Error<br>Messages | TD2 | Checking logs and compliance re-<br>ports for error messages helps to<br>detect anomalies such as an incor-<br>rect parameter definition. |

|                                                                                                   |     | MEASURE<br>COMBINATION                    | TD2 | TCL 2 ▷ Addressed by MXAM<br>ISO 26262 Qualification Kit                                                                                  |

#### 3.3 Tool Qualification

**[E\_MXAM02]**: In chapter 3.2, the need to qualify [UC\_MXAM01] x [E\_MXAM02] is outlined. To qualify this use case-error combination, qualification method c) 'Validation of the software tool' was chosen. A combination of check-specific test cases and reviews was defined to verify that the corresponding checks identify all guideline violations.

For each check, specific test cases for regression, invariant, and smoke tests were designed and implemented as Simulink models. These tests are executed continuously and in the release build pipeline as Jenkins jobs. The check-specific test cases use a common test framework and share a common structure. Each test case consists of eight sub-tests illustrated in Table 5. The resulting JUnit test report (cf. Figure 3) is provided as qualification evidence in the MXAM ISO 26262 Qualification Kit.

Table 5: Common structure of the tests to qualify [UC\_MXAM01] x [E\_MXAM02]

| a) | elementResultsQualifierTest: Qualifiers (type of elements in the check results, such as blocks, lines, etc.) of the elements occurring in the model check results are compared with pre-defined expected results.                                           |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b) | elementResultNameValuePairTest: Name value pairs (check-specific information in addition to the standardized attributes and values, such as name, path, message, etc.) occurring in the model check results are compared with pre-defined expected results. |

| c) | elementResultsPathTest: Path information occurring in the model check results is compared with pre-defined expected results.                                                                                                                                |

| d) | elementResultsResultTest: Verdict of the model check (failed, passed, warning) is compared with pre-defined expected results.                                                                                                                               |

| e) | elementResultResultMessageTest: Messages occurring in the model check results are compared with pre-defined expected results.                                                                                                                               |

| f) | elementResultsSizeCheckTest: Number of the elements results occurring in the model check results are compared with pre-defined expected results.                                                                                                            |

| g) | invariantTest: Results occurring in the model check are compared in two separate analyses.                                                                                                                                                                  |

| h) | elementResultsNotWantedTest: Result occurring in the model check is not aborted.                                                                                                                                                                            |

| Class MATLAB.DynamicTestSuite                                                                        |                                                                                                  |        |          |         |          |                         |         |          |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------|----------|---------|----------|-------------------------|---------|----------|

| Name                                                                                                 | Tests                                                                                            | Errors | Failures | Skipped | Time(s)  | Time Stamp              | Host    |          |

| <u>DynamicTestSuite</u>                                                                              | 327                                                                                              | 0      | 0        | 0       | 2011.217 | 2017-10-<br>12T10:11:18 | Jenki   | nsChecks |

| Tests                                                                                                |                                                                                                  |        |          |         |          |                         |         |          |

| Name                                                                                                 |                                                                                                  |        |          |         |          |                         |         | Status   |

| MATLAB_MATLAB_MAAB.mcheck_db_0151.v01.tests.InvarianzTest_db_0151.invarianzTest                      |                                                                                                  |        |          |         |          |                         |         | Success  |

| MATLAB_MATLAB_MAAB.mcheck_db_0151.v01.tests.InvarianzTest_db_0151.elementResultsNotWantedTest        |                                                                                                  |        |          |         | Success  |                         |         |          |

| MATLAB_MAAB.mcheck_db_0151.v01.tests.ResultTest_db_0151_R2015b.elementResultsQualifierTest           |                                                                                                  |        |          |         | Success  |                         |         |          |

| MATLAB_MAALAB_MAAB.mcheck_db_0151.v01.tests.ResultTest_db_0151_R2015b.elementResultNameValuePairTest |                                                                                                  |        |          |         | Success  |                         |         |          |

| MATLAB_MAAB.mcheck_db_0151.v01.tests.ResultTest_db_0151_R2015b.elementResultsPathTest                |                                                                                                  |        |          |         | Success  |                         |         |          |

| MATLAB_MAAB.mcheck_db_0151.v01.tests.ResultTest_db_0151_R2015b.elementResultSResultTest              |                                                                                                  |        |          |         | Success  |                         |         |          |

| MATLAB.MATLAB_MAAB.mcheck_db_0151.v01.tests.ResultTest_db_0151_R2015b.elementResultMessageTest       |                                                                                                  |        |          |         | Success  |                         |         |          |

| MATLAB_MATLAB_MAAB.mcheck_db_0151.v01.tests.ResultTest_db_0151_R2015b.elementRes                     | MATLAB.MATLAB_MAAB.mcheck_db_0151.v01.tests.ResultTest_db_0151_R2015b.elementResultSizeCheckTest |        |          |         |          |                         | Success |          |

$Figure~3:~JUnit~test~report~to~document~the~qualification~of~[UC\_MXAM01]~x~[E\_MXAM02]~(Excerpt)$

**[E\_MXAM07]**: For the second malfunction [E\_MXAM07], designated, guideline-agnostic test cases have been developed to assess the correct application of parameters. For a baseline version of MXAM, the correctness of the resulting MXAM analysis report has been established manually. For subsequent versions of the tool, regression tests are conducted (cf. Figure 4). With the help of an MXAM report differ, the MXAM analysis reports resulting from a regression test are compared against the analysis reports from the baseline version.

Figure 4: Set-up of system tests and resulting work products to document the qualification of [UC $\_MXAM01$ ] x [E $\_MXAM07$ ].

In addition, 10 system tests covering different aspects of the usage of global, shared, and check parameters were defined as well to qualify [UC\_MXAM01] x [E\_MXAM07] (cf. Figure 5). These system tests are executed continuously and in the release build pipeline as Jenkins jobs. The resulting Allure report (cf. Figure 5) is provided as qualification evidence in the MXAM ISO 26262 Qualification Kit.

| 1  | Req param 01 - check param default                           | 11s 288ms | PASSED |

|----|--------------------------------------------------------------|-----------|--------|

| 2  | Req param 02 - overwrite check param from guideline          | 11s 391ms | PASSED |

| 3  | Req param 03 - overwrite check param from document           | 11s 112ms | PASSED |

| 4  | Req param 04 - overwrite check param from project            | 11s 095ms | PASSED |

| 5  | Req param 06 - default shared param                          | 8s 092ms  | PASSED |

| 6  | Req param 07 - overwrite default shared param from guideline | 8s 115ms  | PASSED |

| 7  | Req param 08 - overwrite default shared param from document  | 8s 285ms  | PASSED |

| 8  | Req param 09 - overwrite default shared param from project   | 8s 068ms  | PASSED |

| 9  | Req param 11 - default global param                          | 8s 003ms  | PASSED |

| 10 | Req param 12 - global adapter param access                   | 11s 007ms | PASSED |

Figure 5: Allure report to document the qualification of [UC\_MXAM01] x [E\_MXAM07].

The guideline-specific tests and the system tests cover the two potential malfunctions used as an example.

Overall, the MXAM ISO 26262 Qualification Kit addresses 17 combinations of use cases and malfunctions that were rated as TCL2 or TCL3 in the tool classification.

#### 3.4 User Activities and Savings

Using a tool-vendor-provided qualification kit can significantly streamline the user's tool classification and qualification activities. However, it does not exempt the tool user from having to perform any further activities.

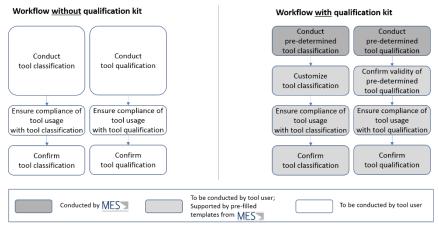

Using the example of the MES Model Examiner®, Figure 6 contrasts the classification and qualification activities to be performed with (right-hand side) and without (left-hand side) the MXAM ISO 26262 Qualification Kit and designates the activities that are being streamlined by using such a kit.

As an example, instead of conducting the entire tool qualification, the user would only need to review and confirm the validity of the documentation of the predetermined tool qualification provided as part of the qualification kit. Regardless of who carries out tool qualification, the user needs to ensure that actual tool usage complies with the constraints and assumptions of tool classification and qualification (e.g., ensuring that the assumed prevention and detection measures are conducted).

If user-created checks are being used, the check-specific qualification activities need to be extended to these checks. As an example, the vendor-provided tests and reviews to qualify ([UC\_MXAM01] x [E\_MXAM02]) need to be augmented by similar tests and reviews for the user-created checks.

Figure 6: Workshare of tool classification and qualification activities.

According to [CF14], the mean effort for tool qualification can be estimated at 80 hours. If a qualification kit is used, the tool user is relieved of most of this effort if the tool usage is sufficiently aligned with the vendor's usage guidance and constraints. In this case, the user's effort is reduced to reviewing and confirming or adapting the pre-determined tool qualification.

Potential savings for the tool user are much higher if the vendor-provided tool qualification removes the need for the user to conduct certain recurring review activities (e.g. the elimination of the recurring review of the parameter specification details [M\_MXAM13]).

The MXAM ISO 26262 Qualification Kit provides the user with designated and flexible Word and Excel templates for the required ISO 26262 classification and qualification work products. User feedback indicates, that such templates are preferred to other available solutions as they are easy to comprehend and adaptation to established, user-specific workflows is straightforward.

#### 4 Summary and Conclusion

Gaining confidence in the tools used to develop E/E systems via tool classification and tool qualification is a base requirement for today's development projects. Modern functional safety standards, such as ISO 26262, call for these activities. The responsibility for conducting these activities rests with the tool user. However, support from the tool vendor can streamline the user activities.

Vendor-provided tool classification already reduces the effort for the user when evaluating the confidence in the tool for the intended use cases. Instead of creating the entire classification, the user only needs to review and confirm or adapt the predetermined tool classification.

However, if the tool classification results in a TCL2 or TCL3 (medium or low tool confidence) for some use cases, users need to apply additional prevention/detection measures or must qualify the tool with respect to these use cases. For some use cases, sufficient tool confidence (i.e., TCL1) can be reached by conducting additional review activities. For other use cases, such additional activities might be infeasible or prohibitive due to high complexity or effort. Tool qualification is the only option here.

Using the example of the MES Model Examiner®, this paper provides insight into the structure and the qualification approach of an actual tool qualification kit for a popular model-based analysis tool. The tool qualification kit utilizes the qualification method 'validation of the software tool'; validation is conducted by a combination of different tests and reviews. Utilizing such a tool-vendor-provided qualification kit significantly reduces the burden on the tool user by minimizing the actual qualification effort and also by reducing the amount of prevention/detection measures they need to carry out.

Further research interests of the authors include a taxonomy of tool classification approaches, the provision of tool classification patterns, and further improvement of the utilized classification and qualification templates.

#### References

[CF11] M. Conrad, I. Fey "ISO 26262 - Exemplary tool classification of Model-Based Design tools". Softwaretechnik-Trends 31 (2011) 3 <a href="http://pi.informatik.uni-siegen.de/stt/31/3/01/Fachgruppenberichte/ada/5-CF11-11\_20110803.pdf">http://pi.informatik.uni-siegen.de/stt/31/3/01/Fachgruppenberichte/ada/5-CF11-11\_20110803.pdf</a>

- [CF14] M. Conrad, I. Fey "Effort and Efficacy of Tool Classification and Qualification". Proc. MBEES X (2014)

- [CF15] M. Conrad, I. Fey "Tool Classification & Qualification According to ISO 26262". 4th Int. CTI Conf. ISO 26262 (2015)

- [CMR10] M. Conrad, P. Munier, F. Rauch "Qualifying Software Tools According to ISO 26262". Proc. MBEES VI (2010)

- [Con10] M. Conrad "Software Tool Qualification According to ISO 26262 An Experience Report". Supplementary Proc. of 21. Int. Symposium on Software Reliability Engineering (ISSRE 2010), pp. 460-466 (2010)

- [Con14] M. Conrad "Tool Classification and Qualification in Practice" 4th VDA Automotive SYS Conference (2014)

- [Con16] M. Conrad, I. Fey "Tool Classification Made Easy The Making of an ISO 26262 Tool Classification Kit". MES User Forum 2016 (2016)

- [CSM11] M. Conrad, G. Sandmann, P. Munier "Software Tool Qualification According to ISO 26262". SAE 2011 World Congress, Detroit, MI, US, April 2011 (2011) doi:10.4271/2011-01-1005

- [DO330] DO-330:2011. "Software Tool Qualification Considerations". RTCA (2011)

- [Glö08] T. Glötzner "IEC 61508 Certification of a Code Generator". ICSS2008 (2008)

- [HK+11] R. Hamann, S. Kriso, K. Williams, J. Klarmann, J. Sauler "ISO 26262 Release Just Ahead: Remaining problems and Proposals for Solutions". SAE 2011 World Congress, Detroit, MI, US, April 2011 (2011)

- [ISO26262] ISO 26262:2011. "Road vehicles Functional safety". Int. Org. for Standardization (2011-2012)

- [KKG10] J. Klarmann, S. Kriso, M. Gebhardt "Qualification of development tools as per ISO 26262". REAL TIMES, 1/2010, pp. 28-20 (2010)

- [Ko18] S. Kohle "MES Model Examiner® Drive ISO 26262 Qualification Kit". Model Engineering Solutions GmbH, <a href="https://www.model-engineers.com/mxam.html">https://www.model-engineers.com/mxam.html</a> (2018)

- [Mai09] M. Maihöfer "Umgang mit Entwicklungswerkzeugen in Software-Entwicklungsprozessen der Automobilindustrie ISO DIS 26262, Band 8, Kapitel 11: Inhalt, Bewertung, Auswirkung und Umsetzung (in German). EUROFORUM Konferenz 'Funktionale Sicherheit nach ISO/DIS 26262', Stuttgart, Germany, Sept. 2009 (2009)

- [SCD+07] I. Stürmer, M. Conrad, H. Dörr, P. Pepper "Systematic Testing of Model-Based Code Generators". IEEE Transactions on Software Engineering, 33 (2007) 9 doi:10.1109/TSE.2007.70708

- [SML08] S. Schneider, P. Mai, T. Lovric "The Validation Suite Approach to Safety Qualification of Tools" Automotive - Safety & Security 2008 (2008)

- [Spä14] A. Späthe "Den Nagel auf den Kopf zu treffen, reicht nicht Carmeq führt die ISO-26262-konforme Klassifizierung von Software-Werkzeugen ein". meilenstein 2/2013, pp. 14-15 (2013) http://www.carmeq.com/downloads/Meilenstein-2-2013.pdf

- [SS07] S. Schneider, O. Slotosch "A validation suite for Model-based Development Tools" 10. Int. Conf. on Quality Engineering in Software Technology CONQUEST (2007)

- [SWP+12] O. Slotosch, M. Wildmoser, J. Philipps, R. Jeschull, R. Zalman "ISO 26262 Tool Chain Analysis Reduces Tool Qualification Costs". Automotive - Safety & Security 2012 (2012)

## Feature-based Recommendation for Product Configuration in the Software Product Lines

Yibo Wang<sup>1</sup>, Lothar Hotz<sup>2</sup>, Matthias Riebisch<sup>3</sup>

**Abstract:** Software Product Line Engineering (SPLE) is a mature technique enabling companies to create individual products in order to meet needs of different customers. In SPLE, Feature Models are the widely used formalism to capture commonality and variability of all products. In Feature Models, program functionalities or other user-visible aspects are represented as Features. In order to configure a product, product line users (such as product managers) select desired features step by step in the Feature Model. However, it is a challenging task in industrial settings, due to high numbers of features and complex interdependency between features. Configuration support is required.

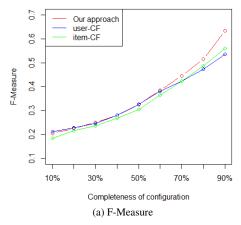

In this paper, we propose a similarity-based recommender system that provides online recommendation during the user's configuration process. Online means that the recommendation result is based on the current feature selections (partial configuration) by the user. In addition, configurations of all previous products are considered as further input data for the recommender system. Unlike other similarity-based recommender systems, we use "Feature Implication" (it implies coexistence of features in the previous configurations) to measure relations between features. A real case study shows that our approach outperforms other state-of-the-art similarity-based approaches in recommendation quality. In other words, it help users not only in finding the correct configuration, but also in making decisions more efficient.

Keywords: Product Configuration; Recommender Systems; Software Product Lines

#### 1 Introduction

Nowadays, mass customization helps companies to meet customer requirements at mass production efficiencies. Software Product Lines Engineering (SPLE) is a mature technique to realize it. SPLE makes it possible to create an individual product by assembling a set of reusable assets. In the domain of SPLE, the Feature Model [Cz12] is one of the most used formalisms, which captures commonality and variability among all products in terms of Features. A Feature [Ka90] is defined as a "prominent or distinctive user-visible aspect, quality, or characteristic of a software system or system". Configuration is one of the most important activities to build an individual product from the product line. In the configuration process, some features will be selected by product line users (followings as users), in order to meet the individual requirements for a customer. But the configuration is more than feature selections. It includes also other activities, such as setting of the feature parameters.

<sup>&</sup>lt;sup>3</sup> University Hamburg, SWK, Vogt-Kölln-Str.30, 22527 Hamburg, riebisch@informatik.uni-hamburg.de

<sup>&</sup>lt;sup>1</sup> University Hamburg, SWK, Vogt-Kölln-Str.30, 22527 Hamburg, Germany, wang@informatik.uni-hamburg.de

<sup>&</sup>lt;sup>2</sup> HITeC, Vogt-Kölln-Str.30, 22527 Hamburg, Germany, hotz@informatik.uni-hamburg.de

However, there exist approaches that change feature parameters into a group of exclusive features [KO14]. So we simplify the configuration as feature selections in this paper.

In industrial settings, a configuration is normally a complex task, because of high number of features and complex feature inter-dependencies. Moreover, the configuration is a gradual and iterative process. In each step some features will be selected (partial configuration). Users often don't have an overview of the whole configuration, due to lack of knowledge about impacts of their feature selections. Thus, automatic support is required to give users some guidances on the current feature selections. They exist in two forms: consistency checking and feature recommendation. Consistency checking is a hard form of configuration support. It ensures the validity of the current feature selections. It means that the feature selections that lead to inconsistency are not permitted. On the contrary, recommendation is a soft form. It provides only suggestions (e.g. "you should consider the feature 'X', because it exists in most of the previous configurations"). But these suggestions can be ignored. In this paper, we concentrate on the recommendation part and show how to integrate it with the existing consistency checking approaches (such as SAT solvers).

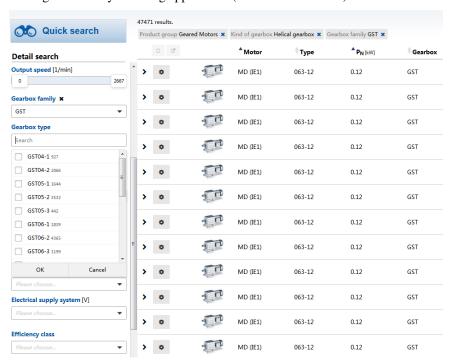

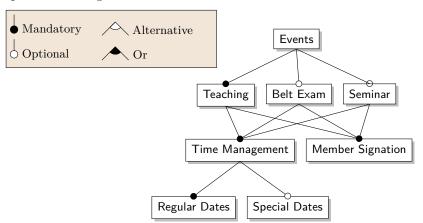

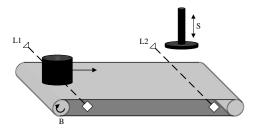

Fig. 1: Lenze configurator

In addition, our research is inspired by the Lenze configurator (Figure 1). In the configurator, if some options have been decided ("GST" selected as Gearbox family), we ask if it is

possible to provide suggestions for other options (recommend "GST06-2" as Gear type), in consideration of the set of all available product variants?

[Pe16] follows the similar ideas to provide recommendations. The authors suggest to use the standard recommenders, such as similarity-based Collaborative Filtering (in the following referred to as CF) and Bias Regularized Incremental Simultaneous Matrix Factorization (in the following referred to as BRISMF), because they provide better recommendation results than other state-of-the-art ones. Our approach goes a step further by adapting the standard recommendation algorithm CF to the specific problem, namely to the feature selection problem.

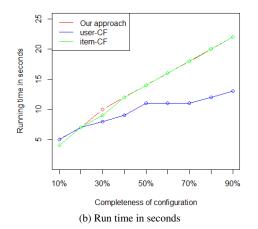

The contributions are summarized as follows. First we propose a similarity-based feature recommender system, by using "Feature Implication" derived from previous configurations to generate recommendations. Second, we design a tool support by extending a state-ofthe-art recommender system. Last but not least, we evaluate the tool (in precision/recall and run time) with a real-world data set. The results show that it provides more precise recommendation results than the traditional similarity-based approaches.

#### 2 **Background**

#### 2.1 Product-Line Engineering

SPLE defines two main processes, namely the Domain Engineering and the Application Engineering. The Domain Engineering consists of the activities such as domain analysis, setting up feature model and preparation of reusable assets. The Application Engineering consists of the activities like requirements analysis, product configuration and product generation and integration.

A Feature Model consists of the feature diagram [Ka90] and other additional information such as Cross-Tree Constraints. A feature diagram is a graphical tree-like representation that shows the hierarchical organization of features (such as "mandatory", "optional" and "feature groups"), while Cross-Tree Constraints define relations among hierarchical not directly connected features (such as "requires" and "excludes"). The Feature Constraint is a generic term that refers to any type of existing feature relationship among features (hierarchical relationship plus cross-tree constraints). A configuration with respect to a given Feature Model is represented as an arbitrary combination of features. A configuration is valid in respect of a Feature Model, if and only if all the Feature Constraints are hold. In the Application Engineering, users must choose which features they want to have for an individual product. In this context, this decision process is also referred to as configuration.

#### 2.2 **Recommender Systems**

Recommender Systems provide personalized recommendations for users in making decisions. According to the type of information available for making recommendations, they

can be divided into 3 groups: Collaborative, Content-based and Knowledge-based recommendation. Collaborative recommendation approaches exploit information about the past behaviour or the opinions of an existing user community for predicting which items the current user will most probably interested in [Ja10]. While Content-based approaches are based on the availability of item descriptions and a profile that assigns importance to these characteristics, Knowledge-based approaches exploit additional and means-end knowledge such as constraints to generate recommendations [Ja10].

Collaborative recommendation is the most researched and used recommendation approaches in the recent years. User-based Collaborative Filtering (CF), item-based CF and Matrix factorization are the most important recommendation techniques in this category. The first two approaches calculate recommendations directly from the user-item ratings. While user-based CF compute recommendations using the similarity between users, item-based CF makes use of the similarity between items. Item-based CF is more apt for offline preprocessing and large-scale problems. Unlike CF, Matrix Factorization (MF) approaches must firstly learn from the user-item ratings and then uses the learned model (latent factors) to make predictions. In general, CF approaches provide more precise results than MF approaches, because the full ratings are used for generating the recommendations [Ja10].

#### 3 The proposed approach

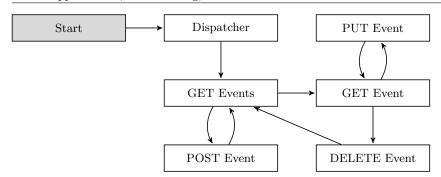

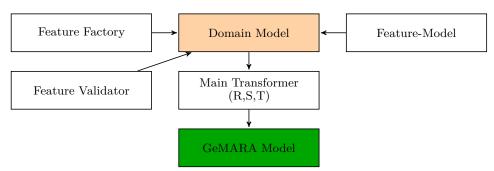

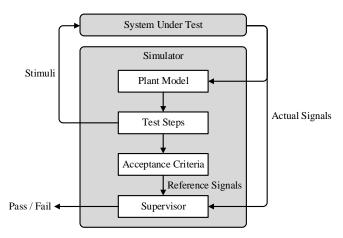

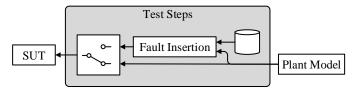

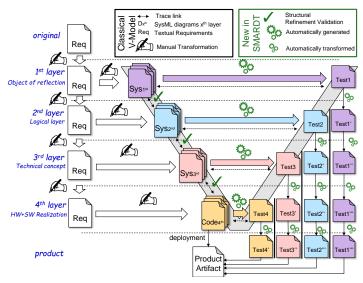

#### **Configuration Process with Recommendation Support** Object Tool Previous Matrix LEGENI Transformato configurations Recommendation results Configuration Feature Incorrect feature Propagator selections configuration (SAT-Solver) Constraint Solver Feature (SAT-Solver) Model Changes in Configurator configuration Requirements

Fig. 2: Configuration process with recommendation support

To start with the configuration process, users should select/deselect features in a configurator (such as EngCon [Kr13], pure::variants [Be08], or FeatureIDE [TKB14]), according to

their individual requirements. The configurator presents the feature model graphically and enables interaction with users. The feature selections could lead to some changes in a configuration. Then, its validity will be checked by the constraint solver. If it is invalid, incorrect feature selections will be shown in the configurator and should be corrected by users. Otherwise, the feature propagator starts to propagate the user's selections onto other features. The current configuration after feature propagation (the lower part of Figure 2) becomes one part of the input for the recommender. The other part (the upper part of Figure 2) comes from the matrix transformation of previous configurations (more details in the following sections). Finally, the recommendation results will be generated by the recommender and given to users. Thus, the recommendations will be considered in the further configuration iterations.

#### **Choosing Recommender Techniques**

In our approach, one input for the recommender system are previous configurations. They are very similar to user-item ratings in the similarity-based collaborative filtering approaches. Thus, we initially choose Collaborative Filtering (in the following referred to as CF) as our recommender technique. Because of poor scalability in processing large numbers of configurations in the user-based CF, our approach is based on the item-based CF. In addition, we don't use Matrix Factorization techniques (such as BRISMF in [Pe16]) to improve the recommender, due to its poor performance in respect of run time (waiting time of over 30 seconds to generate a recommendation), In realistic scenarios, users should get a recommendation instantly after the current configuration step.

#### Formal Definition

In this section, we describe the formal representation of a configuration and definitions for feature recommendation. We follow the basic definitions in [Pe16] and make some amendments and extensions.

A **feature model**  $\mathbb{FM} = (\mathbb{F}, \mathcal{R})$  consists of a tuple of feature states  $\mathbb{F} = \{-1, 0, 1\}^h$  and a set of feature constraints  $\mathcal{R} = \{r_1, r_2, \dots, r_m\}$ , where h is the number of features and m the number of constraints. A **feature** has the **state** 1 if it has been selected (*positive decided*); -1 if it has been deselected (negative decided); 0 if it is has not been decided (undecided). A **configuration**  $\vec{c}$  for a given feature model FM is a tuple of states for all features, more formally as  $\vec{c} = \{f_1, f_2, \dots, f_h\}$ . A configuration is **complete**, iff each feature has a decided state (state= -1 or 1). A configuration is **partial**, iff it is not complete. In other words, it still has some features in undecided states (state=0). According to their states, features in a configuration can be divided into 3 groups: PD (positive decided), ND (negative decided) and UD (undecided), such that PD  $\cap$  ND  $\cap$  UD =  $\emptyset$  and PD  $\cup$  ND  $\cup$  UD =  $\vec{c}$ . **Previous configurations** (in the following referred to as PC) are a collection of valid configurations from all existing products. In our work, it is represented as a matrix of n rows h columns, where n is the number of previous configurations and h the number of features. Thus, each row represents an existing configuration.

$$PC = \begin{bmatrix} pc_{11} & pc_{12} & \dots & pc_{1h} \\ \vdots & \vdots & \ddots & \vdots \\ pc_{n1} & pc_{n2} & \dots & pc_{nh} \end{bmatrix}$$

(1)

Besides feature constraints directly defined in the feature model, additional feature relations could also be derived from PC. We call this type of feature relations as **feature implication**. Given two features  $f_x$  and  $f_y$ , it gives a hint on how likely  $f_y$  should also be selected, if  $f_x$  has been selected [Ma14]. It is also known as the confidence between two items in the Market Basket Analysis [TSK05]. The feature implication is reflexive and asymmetric. More formally, it is defined as<sup>4</sup>:

confidence

$$(f_x \stackrel{\text{is given}}{\to} f_y) = \frac{|f_x \text{ and } f_y|}{|f_x|}$$

(1)