Hierarchical Platform Architecture

The hierarchical platform architecture can be used to model multicore architectures in terms of their execution units (e.g., processors, cores), topology, memories, and I/O ports. It is organized into the following layers:

- Cluster level: A cluster represents an entire distributed system. This modeling level describes the available clusters and their interconnections.

- Node level: This level provides a model of the internals of a single cluster, i.e., the structural elements and the topology of a physically distributed computer system.

- Tile level: This level models the internals of a single node. A model at the tile level describes the structural elements of a multi-processor system on-chip whose elements are interconnected by an on-chip network.

- Core level: This level describes the internals of a single tile, i.e., busses, cores, memories and network interfaces.

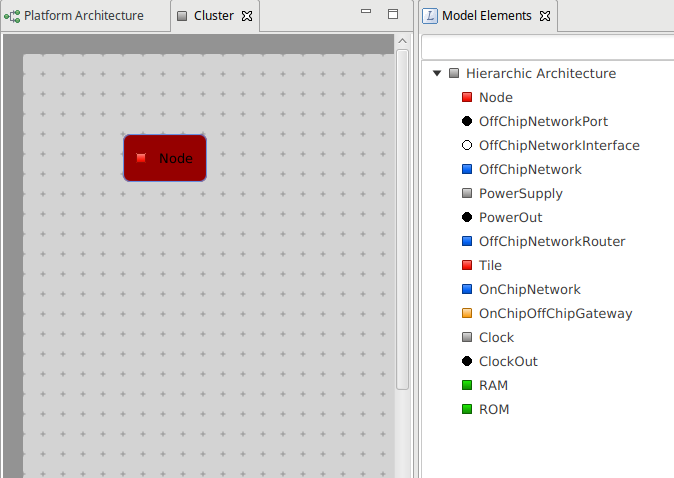

When modeling a hierarchical platform architecture, it should be noted that the Model Elements library offers model elements from both the current level (the Node level in the example below) and the elements at the next level (here: the Tile level). Elements from the current level can be added directly to the edited platform element (here: the internals of a Cluster), whereas elements from the next element can be dropped into the elements from the current level (e.g., a Tile can be dropped into a Node).

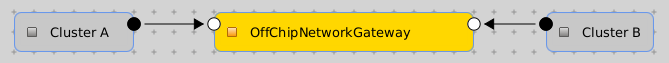

Cluster level

This modeling level is optional. If it is present, a model at the Cluster level provides elements to describe logical groups of physically distributed computer systems based on the entities listed below. Otherwise, Nodes are contained directly by the Platform Architecture and are assumed to be part of a single cluster.

- Cluster: A cluster, i.e. a (logical) group of Nodes that are connected via an OffChipNetwork (see node level).

- OffChipNetworkGateway: A GatewayUnit providing a bridge between the OffChipNetworks of connected Clusters.

In the figure below, a simple model consisting of two Clusters can be seen. Both Clusters are connected via an OffChipNetworkGateway. The Clusters have attached OffChipNetworkPorts (connectors represented by black circles) which are each connected to an OffChipNetworkInterface of the contained OffChipNetwork and to the OffChipNetworkInterface of the OffChipNetworkGateway element. In this example, a connection between the internal OffChipNetworks of Cluster_A and Cluster_B is modeled.

Node level

The Node level provides a model of the internals of a single cluster, i.e., the structural elements and the topology of a physically distributed computer system. It consists of the following modeling entities:

- Node: An electronic control unit (ECU) / a computer hosting a multi-core chip containing Tiles connected by a network-on-chip

- OffChipNetwork: An off-chip network to interconnect multiple Nodes.

- OffChipNetworkRouter: A router or switch of an OffChipNetwork.

- Power Supply: Model element representing an individual (independent) power supply.

- Clock: Model element that represents clock sources.

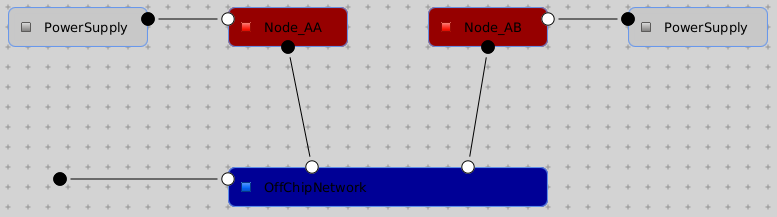

The figure below shows an example model of the Node level where the internal structure of a Cluster consists of two Nodes, one OffChipNetwork, and two PowerSupplys. The OffChipNetwork has three attached OffChipNetworkInterfaces. Three OffChipNetworkPorts (represented by black connectors) at the Nodes and at the right hand side of the OffChipClusterGateway are connected to these OffChipNetworkInterfaces. The NetworkInterface located at the left side of the OffChipNetwork in the example is connected to an OffChipNetworkPort of the containing Cluster.

Tile level

The Node level provides a model of the internals of a single node, i.e., the structural elements of a multi-processor system on-chip whose elements are interconnected by an on-chip network. It consists of the following modeling entities:

- Tile: A tile, i.e. a multi-core or single-core processing unit that is connected to the OnChipNetwork via its OnChipNetworkPort.

- OnChipOffChipGateway: A gateway from the on-chip to the off-chip level.

- RAM: Model element to describe volatile off-chip memory.

- ROM: Model element to describe read-only, non-volatile off-chip memory.

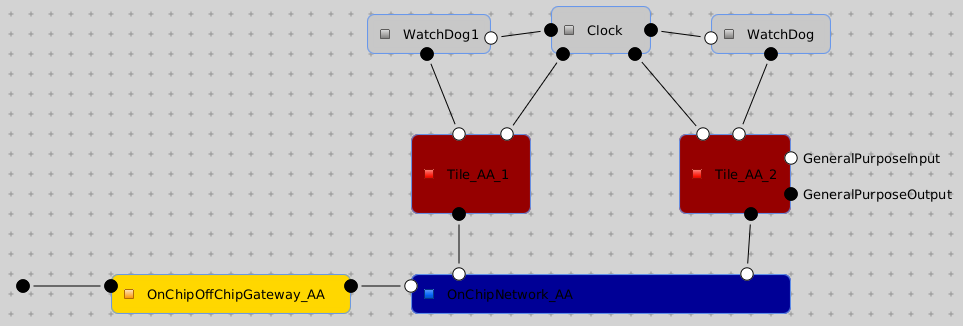

The figure below shows an exemplary model at the Tile-level, i.e. the internal structure of a Node. There are two Tiles, one OnChipNetwork, and an OnChipOffChipGateway. The white connectors attached to the OnChipNetwork represent the OnChipNetworkInterfaces. Likewise, the connectors attached to the Tiles and at the right hand side of the OnChipOffChipGateway represent OnChipNetworkPorts that are connected to the corresponding OnChipNetworkInterfaces of the OnChipNetwork.

The OnChipOffChipGateway depicts the gateway of the OnChipNetwork shown in this example to the network at the containing layer (i.e., an OffChipNetwork at the Node layer). The connector in the very bottom left of the figure represents the OffChipNetworkPort of the Node that contains the model shown in the figure. It is connected to an OnChipOffChipExport (left connector of OnChipOffChipNetworkGateway) that is used to model the connection to the containing Node's OffChipNetworkPort.

In the example, a common Clock source provides a clock signal via ClockOuts to the connected Tiles which receive the signal via the attached ClockIns. Furthermore, WatchDogs are connected to the two present Tiles via WatchDogOuts (at the WatchDogs) and WatchDogIns (at the Tiles). Since WatchDogs are essentially timers, they require a clock signal and, hence, they are connected to the Clock that provides the signal to the Tiles. The Tile Tile_AA_2 additionally has an attached GeneralPurposeOutput port and a GeneralPurposeInput port that model generic GPIOs of processors or boards.

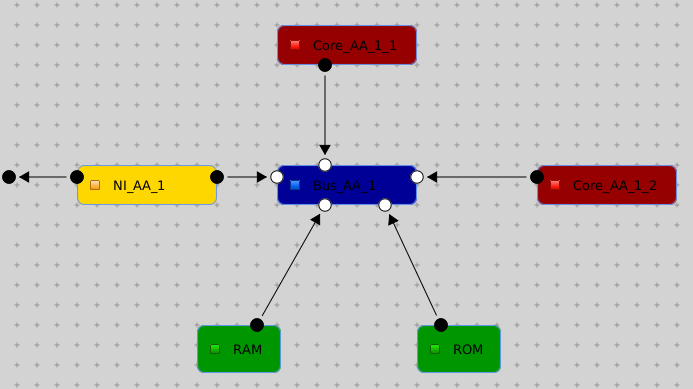

Core level

The Core level provides a model of the internals of a single tile, i.e., structural elements such busses, cores, memories and network interfaces. It consists of the following modeling entities:

- Core: Structural model element used to describe a single core of a processor.

- Bus: Model element describing the (main) communication resource on processor level which connects cores, memories and network interface.

- NetworkInterface: Model element that connects the processor elements to the OnChipNetwork via a BusOnChipNetworkExport to which this Tile is connected.

- RAM: Model element to describe volatile on-chip memory.

- ROM: Model element to describe read-only, non-volatile on-chip memory.

The figure below contains an exemplary model at the Core level, i.e. the internals of a Tile. The model contains two Cores, one RAM and one ROM, a Bus, and a NetworkInterface. All mentioned elements are connected via the Bus. The ports (black connectors) attached to the Cores and to the NetworkInterface are MasterPorts since they need to be able to initiate communication via the Bus. These MasterPorts are connected to BusMasterInterfaces, and thus, the model elements mentioned above are able to communicate. In contrast, the memory elements are connected via BusSlavePorts to the BusSlaveInterfaces of the Bus, as these elements do not initiate any communication (passive elements). The left hand side of the NetworkInterface is a model of the gateway to the OnChipNetwork at containing layer (i.e., to the Node layer). The left-most black connector is the OnChipNetworkPort of the Tile that contains the discussed example model. This Port is connected to the NetworkInterface's OnChipNetworkExport (left connector of NetworkInterface component) that depicts the interface of the processor level to the on-chip-network.